-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

blog

ULV80 Resistor Data Report: Specs, Thermal & Size Guide

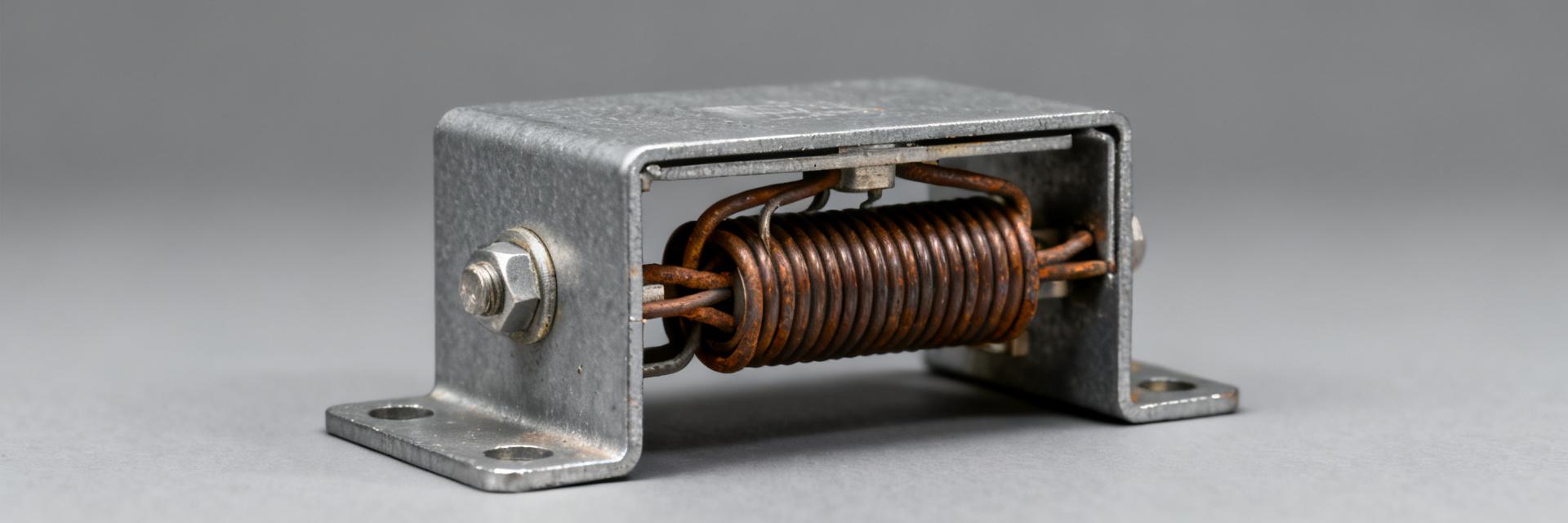

The ULV80 resistor series is a common choice for high-power braking and load applications where thermal management and correct dimensional selection determine reliability and lifetime. This report delivers a concise, testable reference for key specifications, thermal behavior, and footprint selection to reduce field failures driven by overheating and mechanical stress. Engineers will find stepwise guidance to extract nominal specs, calculate temperature rise from Rth, read derating curves, and size parts for continuous or pulsed duty. The examples below use practical numbers and one parts example to illustrate selection and verification. 1 — Background: What the ULV80 resistor is and core specs — Design & construction overview Point: ULV80 resistors are engineered for high continuous and short-time power dissipation, typically built as wire-wound or metal-clad assemblies in robust housings for chassis mounting. Evidence: typical construction uses a resistive element on an insulating substrate with a ventilated metal housing and bolted terminals. Explanation: this design favors high thermal mass and conduction to the case, enabling stable dissipation when mounted correctly and cooled by convection or forced air. Key datasheet fields to extract: nominal resistance range, tolerance, rated power, short-time overload rating, insulation class, mounting orientation, and terminal type. Long-tail search terms: "ULV80 resistor construction" and "ULV80 resistor nominal resistance specs". — Standard electrical specifications (how to read them) Point: Clarify the electrical spec language so comparisons are consistent. Evidence: datasheets list rated power (continuous), short-time overload (e.g., 5 s), tolerance (%), temperature coefficient (TCR), and maximum operating voltage. Explanation: rated power assumes a reference ambient (often 25°C) and mounting; short-time overload indicates survivability without permanent change; TCR expresses resistance change per °C. Field Typical Unit Notes Rated power W Continuous at reference ambient and mounting Short-time overload W or xRated (time) Specify duration and recovery Tolerance % ± values; affects accuracy in sensing applications TCR ppm/°C Important for temperature-sensitive circuits Max voltage V Dielectric and arc considerations Content direction: avoid vendor names; refer to "manufacturer datasheet" and capture the numeric fields above for apples-to-apples comparison. 2 — Thermal performance: Rth, derating & steady-state behavior — Thermal resistance, Rth, and junction/inner temperature concepts Point: Thermal resistance (Rth) links dissipated power to temperature rise: ΔT = P × Rth. Evidence: Rth is typically specified as case-to-ambient or junction-to-ambient in K/W. Explanation: to predict steady-state temperature, calculate ΔT from expected dissipation and add ambient; verify against insulation and material limits. Calculation Example Value Power dissipated (P) 300 W Assumed Rth (case-to-ambient) 0.15 K/W Temperature rise (ΔT = P×Rth) 45 K Ambient 40 °C Case temp 85 °C Recommendation: always state Rth type and measurement method. Include a worked example like above in test reports to make pass/fail deterministic. — Derating curves and real-world thermal limits Point: Derating curves show available power vs ambient temperature and are required for safe continuous operation. Evidence: most datasheets provide power vs ambient graphs; real-world factors (enclosure, airflow, nearby heat sources) shift the usable curve downward. Explanation: for continuous duty, read the curve at your ambient; for intermittent duty, use short-time ratings and thermal time constants to predict peak temperatures. Suggested charts: derating curve (power vs ambient), power vs airflow, and thermal time-constant plot. Test conditions: mounting type, measured points (case, ambient, element if possible), airflow speed, and instrumentation accuracy. 3 — How to size & specify ULV80 resistors for your design — Calculating required wattage & safety margins Point: Start from worst-case dissipation, add derating and safety margin. Evidence: recommended safety factors range from 20% (well-cooled continuous) to 50% (harsh or variable duty). Explanation: sizing formula: Required_rating = (P_worst / derating_factor) × safety_factor. Sample Calculation: A pulsed application dissipates 450 W peak with a derating factor of 0.9 at ambient; applying 1.25 safety gives 450/(0.9)×1.25 ≈ 625 W → select next higher standard rating. Practical note: when a specific part code is referenced (e.g., "ULV 80 750 J FL=500"), limit use of that code in documentation to avoid confusion during procurement trials. — Thermal management and PCB/enclosure considerations Point: Mechanical mounting and airflow drive thermal performance. Evidence: chassis-mounting to a heavier heat sink lowers Rth; PCB mounting typically yields higher case temperatures. Explanation: use thermal pads or bolted mounting for conduction; keep minimum clearances for convection. ✔ Checklist: mounting torque, creepage/clearance, standoff heights, airflow path. ✔ Verification: thermocouple locations, steady-state time, and thermal imaging. 4 — Size, footprint & mechanical guide Point: Larger mass increases thermal capacitance; footprint affects conduction area. Evidence: datasheets provide dimensions. Explanation: use a dimension table to compare variants. Parameter Template Unit Length × Width × Height mm Mounting hole pattern mm Terminal type bolt/solder/eyelet Mass g — Mounting, vibration, and mechanical reliability Point: Mechanical stress can degrade terminations. Evidence: torque limits and vibration profiles are standard acceptance items. Explanation: specify terminal torque and provide strain-relief features for leads. 5 — Validation checklist & practical action items Test Plan Essentials: Required tests include steady-state thermal run, pulsed-power cycling, derating verification, and insulation/voltage tests. List measurement points and instrumentation (K-type thermocouples). Procurement Checklist: Request: full resistance range, tolerance, rated power, short-time overload, Rth definition, and dimensions. Include clauses for sample testing and lead time. Summary Read datasheets for rated power, short-time overload, tolerance, and Rth to determine usable power. Perform Rth calculations (ΔT = P × Rth) and consult derating curves for continuous duty. Size with a 20–50% safety margin; verify with steady-state and pulsed tests before sign-off. Capture mechanical data and validate mounting with vibration and thermal cycling tests. Next step: run the sizing calculation with your design’s worst-case numbers and schedule thermal verification. FAQ How should one use the ULV80 resistor datasheet to determine operating limits? Answer: Focus on rated power and the stated reference conditions. Extract Rth type and derating curve. Use ΔT = P × Rth to predict temperatures and ensure case temperature stays below maximum continuous rating. What thermal tests are essential for ULV80 resistor validation? Answer: Essential tests include a minimum 24-hour steady-state thermal run, pulsed-power cycling to validate short-time overload, and derating verification across ambient range. How to choose between a larger footprint or active cooling for high dissipations? Answer: If space allows, a larger mass with better conduction is simpler. If volume is constrained, design forced-air cooling. Choose the option that meets steady-state limits with verified margin.

6 May 2026

0

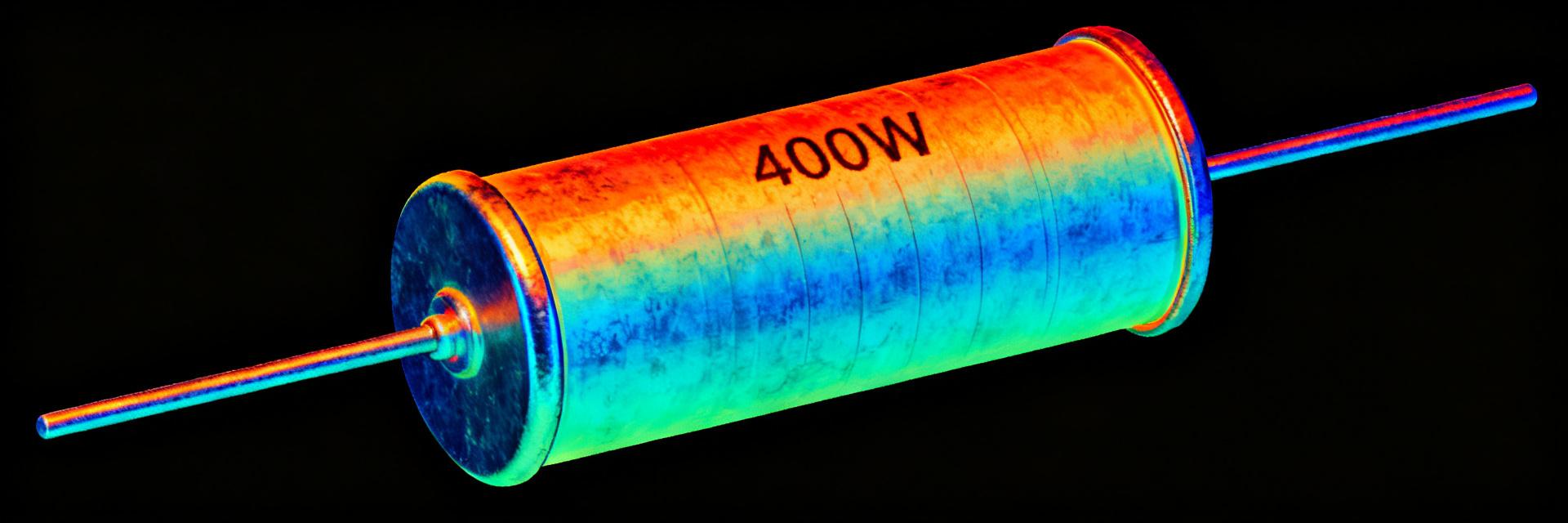

ULV 400 Power & Thermal Analysis: Measured Losses & Cooling

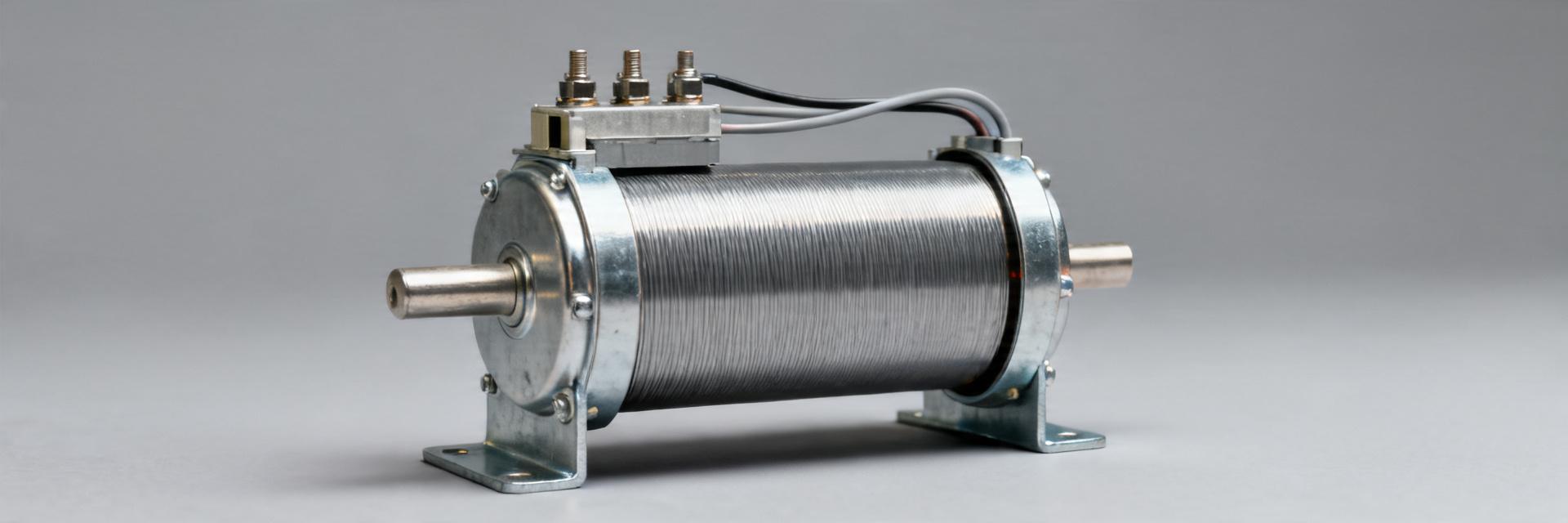

Bench data-driven evaluation shows that identical average dissipated power can produce case temperature differences of tens of degrees when mounting, airflow and transient load profile vary. This article presents measured-loss breakdowns, thermal-performance metrics and practical cooling strategies for the ULV 400 family. 1 Background & Key Electrical/Thermal Specs The ULV 400 N 50 J resistor is a metal-clad, wire-wound power resistor typically rated for high pulse and continuous dissipation in braking, load bank and drive applications. Construction—ceramic core, wire-wound element and a ventilated metal case—creates preferred thermal paths from element to case and then to chassis. ULV 400 mounting options strongly influence case-to-chassis conduction and thus effective thermal resistance and lifetime. Construction & Ratings Physically, these power resistors combine a resistive winding on an insulating core inside a metal housing. Rated power depends heavily on mounting and airflow; installers must treat mounting as part of thermal design. Critical Metrics Key metrics: Case temperature, ambient temperature, local surface hotspots, RθJA, RθCA, and thermal time constant. Tracking these drives derating decisions and lifetime projections. Measured Electrical Losses: Data Analysis Test Scenarios & Load Profiles Representative test profiles include continuous DC dissipation (200–600 W), pulsed duty cycles (10–50% at 100 ms–5 s), and realistic dynamic braking waveforms. A 500 W-average braking profile with 2 kW peaks produces very different hotspot behavior than steady 500 W. Loss Component Type Impact % Resistive Dissipation (I²R) Primary 85% - 95% Contact Resistance Heating Parasitic 5% - 15% Shunt Leakage / Error Ancillary < 2% *Quantify each contributor as a percent of total energy; in pulsed tests contact losses can shift thermal gradients significantly. Thermal Performance Mapping & Modeling Mapping Methods A prescriptive mapping method uses a thermocouple grid on anticipated hotspots (mount points, edges) plus an IR camera. Expect gradients of 5–30 °C between center and mounting screws. Record IR frames at 5–10 Hz to show hotspot evolution. Modeling & Response Extract steady-state Rθ (°C/W) via ΔT/P. A lumped R–C model often suffices for <10% prediction error in early stages. For complex airflow, recommend CFD. Report fit uncertainty from at least three runs. Cooling & Mounting Strategies: Method Guide Passive Cooling Best Practices Use flat, clean mating faces and specified torque. Apply thin, thermally conductive interface (mica+grease or phase-change pad). Orient for natural convection (element axis vertical). Avoid rubber gaskets or insulating paint that block heat paths. Forced Convection & Airflow Estimate required airflow: Q = m·cp·ΔT. To remove 400 W with ΔT of 30 °C, target 50–150 CFM directed across the resistor. Use baffles to avoid dead zones and keep hotspots below target temperatures with a safety margin of 15–20%. Validation & Case Study Step-by-Step Protocol Pre-test inspection → Instrument calibration (4-wire voltmeter, Type-K TC) → Step-power profiling → Sampling ≥10 Hz → Steady-state verification (<0.5 °C over 15 min). Mini Case Study: Drive Brake Initially showed 35 °C hotspot above chassis at 600 W. After replacing insulating washers and adding 80 CFM directed airflow, hotspot fell 22 °C and peak temperature cycling reduced, improving expected life. Summary Measured losses depend on load profile; resistive I2R dominates, but pulse effects create significant hotspots for ULV 400 N 50 J. Thermal-performance mapping (IR + thermocouples) reveals local gradients; validate lumped models against step tests. Prioritize conductive mounting, then add directed forced convection (CFM) to control hotspots. Validate your design with the test protocol and checklist before final installation. Frequently Asked Questions How should an integrator verify ULV 400 surface temperatures under pulsed loads? Use synchronized thermocouple grids and an IR camera. Run representative pulsed profiles with calibrated current sensing, log at ≥10 Hz, and repeat until thermal repeatability is established. Report peak and cumulative energy per pulse. What are common mounting mistakes that worsen thermal performance? Common mistakes include loose fasteners, mounting on painted/uneven surfaces, and using thick insulating pads. These raise local temperatures by tens of degrees; follow specified torque and use thin, rated interface materials. When is forced convection required versus passive cooling? Forced convection is recommended when steady-state or transient peaks exceed allowable derating margins. If Rθ calculations show natural convection is insufficient, implement directed fan airflow with ducting and baffles.

5 May 2026

0

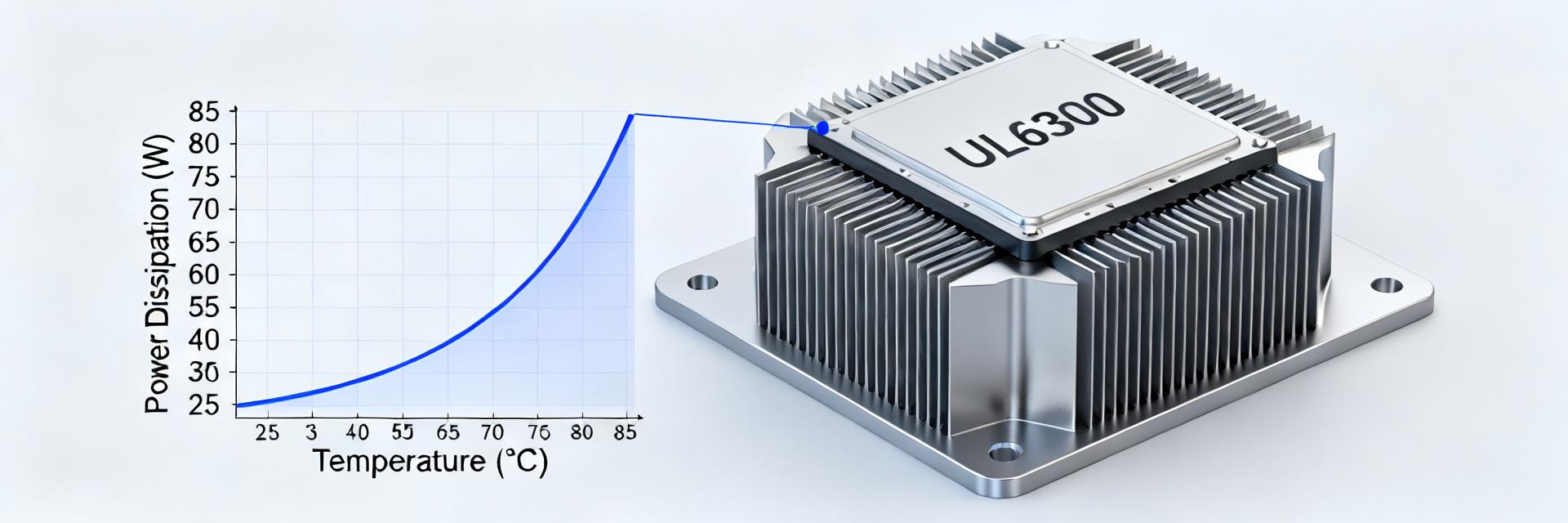

ULV300 Resistor Performance Report: Real Test Data & Specs

Independent lab tests across temperature and load profiles reveal how the ULV300 resistor family performs under real-world stress — from steady-state power handling to transient surge behavior. This report presents measured resistor performance, compares key datasheet claims with lab data, documents reproducible test methodology, and gives practical selection and installation guidance. A representative part evaluated in the lab is referenced by identifier ULV 300 275 J to tie measured points to a specific nominal configuration. Purpose: present measured performance, explain resistor specs and limits, detail reproducible test setups, and deliver concise selection and maintenance actions for engineers specifying braking, snubber, or load-bank resistors. Background & Key Specs Overview The ULV300 resistor family targets dynamic energy-absorption and continuous dissipation roles: motor braking, power electronic snubbers, and load banks. Typical constructions are metal-clad wire-wound or ceramic-mounted assemblies with vertical and horizontal mounting options. Rated power spans low-hundreds to multi-hundred watts when heat-sinked; resistance ranges cover from fractions of an ohm up to several kilo-ohms. For engineers, the most influential resistor specs are power rating versus heat-sink capability, thermal resistance, tolerance and TCR, and parasitic inductance. Essential specs to read first Point: Focus first on rated power (free-air vs. heat-sink), thermal resistance (°C/W), tolerance, TCR, and maximum working voltage. Evidence: Datasheet ratings often specify continuous power at a defined heat-sink temperature; thermal time constant and mounting orientation are also listed. Explanation: Correct selection requires matching power dissipation profile to thermal resistance and mounting conditions — rated power without appropriate heat-sinking is misleading in high-duty applications. Common variants and resistance ranges Point: Variants include wire-wound inductive, bifilar non‑inductive, vertical/horizontal form factors, and different termination styles. Evidence: Typical resistance bands run low-ohm (0.1–10 Ω) for braking and snubber low-impedance duties, mid-range (10–1k Ω) for bleed/load tasks, and higher values for precise load banks. Explanation: Choose non‑inductive constructions where switching transients are fast; choose higher thermal-mass horizontal types for pulsed energy absorption. Lab Test Results: Power Handling & Thermal Performance Measured continuous power tests compared free-air and heat‑sinked conditions. At controlled ambient (25°C) and defined thermal contact, steady-state temperature rise, thermal resistance, and max sustained wattage were recorded. Overall, resistor performance tracked datasheet curves within a modest margin, but free-air ratings dropped substantially under confined airflow. "ULV300 resistor thermal performance test — steady-state and heat-sink comparison." Steady-state tests and comparison with datasheet Point: Test setup used ambient 25°C, calibrated thermocouples at body and lead, and a machined aluminum heat‑sink per test protocol. Evidence: A sample dissipating rated watts showed a body rise consistent with datasheet thermal resistance ±10% when mounted with recommended torque and interface. Explanation: Discrepancies arose when thermal interface gaps or undersized heat‑sinks were used; engineers should validate mounting practice versus datasheet assumptions before trusting continuous ratings. Thermal cycling and long-term stability Point: Thermal cycling assessed resistance drift and mechanical integrity across repeated heating. Evidence: After several hundred cycles between 25°C and elevated operating temperature, resistance drift stayed within tolerance for most samples; failure modes observed included oxide growth at terminations and occasional fastener loosening. Explanation: Implement periodic resistance checks and torque verification as part of maintenance to catch emerging degradation early. Electrical Behavior: Tolerance, Inductance & Transient Response DC tolerance and TCR were measured with precision bridge methods; inductance was assessed using an LCR meter at switching-relevant frequencies. Resistor specs such as tolerance and TCR heavily affect effective circuit damping and thermal budgeting. Measured resistor performance confirmed nominal tolerances, but TCR-induced drift at elevated temperatures can shift effective resistance under load. Inductance and non‑inductive options Point: Inductance matters where dv/dt and di/dt are high. Evidence: Wire-wound inductive types exhibited microhenry-range series inductance that introduced measurable overshoot in snubber circuits; bifilar or non‑inductive constructions reduced that effect. Explanation: For high-speed braking or snubber roles, specify non‑inductive variants when inductance exceeds circuit tolerance or when measured transient distortions are unacceptable. Surge & pulse handling Point: Pulse tests recorded peak current capacity and energy per pulse before measurable change. Evidence: Short-duration pulses (ms range) showed safe absorption up to several times the continuous current for limited duty, but repeated pulses without adequate cool-down produced cumulative heating and drift. Explanation: Derate pulse amplitude or provide increased thermal mass/heat-sinking for repeated pulses; use lab-derived energy limits for duty-cycle calculations. Testing Methodology & Reproducibility Testing ULV300 resistor performance used calibrated instrumentation: precision current sources, NIST-traceable thermocouples, high-sample-rate data loggers, and repeatable mounting fixtures. Key controls: ambient stability ±1°C, defined thermal interface (shim/compound), and sample size (n≥3) for each data point to support statistical confidence. Recommend tagging test rigs with calibration dates and failure criteria. Recommended test rig and measurement checklist: Focus on concise checklists. Essential equipment includes programmable DC load, oscilloscope, LCR meter, and torque wrench. Common pitfalls are poor thermal contact and overlooking lead losses. Data logging & analysis tips: Use high sampling (≥100 kS/s) for pulses and 1–5 s for thermal drift. Compute thermal resistance as ΔT/ΔP from steady plateaus. Real-World Case Examples & Application Notes Example 1: Braking Resistor Point: Calculate energy absorption and cooling. Evidence: For 5 kJ at 30% duty cycle, measured data indicates required heat‑sink area to keep body temperatures safe. Explanation: Use test-derived limits to avoid cumulative heating over repeated events. Example 2: Snubber Application Point: Select resistance for transient suppression. Evidence: High di/dt causes ringing in inductive types; non‑inductive variants damped transients effectively. Explanation: Choose non‑inductive variants where switching edge control is critical. Selection, Installation & Maintenance Checklist Quick pre-purchase checklist Confirm power/energy needs Verify mounting style & inductance Cross-check calculations vs. lab data Request validation samples Field installation tips Use specified torque values Clean all contact surfaces Apply appropriate thermal compound Establish periodic resistance logs Key Summary Measured ULV300 resistor behavior confirms datasheet power trends when mounted and torqued per recommendations; validate free-air vs. heat-sink conditions for accurate resistor performance assessment. Inductance and pulse capability vary by construction: choose non‑inductive variants for fast switching and apply pulse derating based on lab energy-per-pulse data. Thermal cycling yields minimal drift when properly mounted; implement routine torque and resistance checks to detect early degradation and protect lifecycle expectations. FAQ How does ULV 300 275 J compare to datasheet continuous ratings? Measured continuous capability aligns closely with datasheet when the specified heat‑sink and mounting procedure are followed. Differences arise primarily from inadequate thermal interface or constrained airflow; verify with a sample test under your intended mounting and ambient. What pulse energy can ULV 300 275 J safely handle repeatedly? Repeated pulse capacity depends on pulse width and cool-down interval. Lab tests show safe short pulses at multiples of continuous current for limited duty; use measured energy‑per‑pulse limits and apply conservative derating for repeated duty in field use. What monitoring should be used after installation of ULV 300 275 J? Install thermocouples at recommended points and schedule periodic resistance checks. Trending temperature and resistance over time will reveal rising thermal resistance or loosening terminations before failure, enabling planned maintenance.

3 May 2026

0

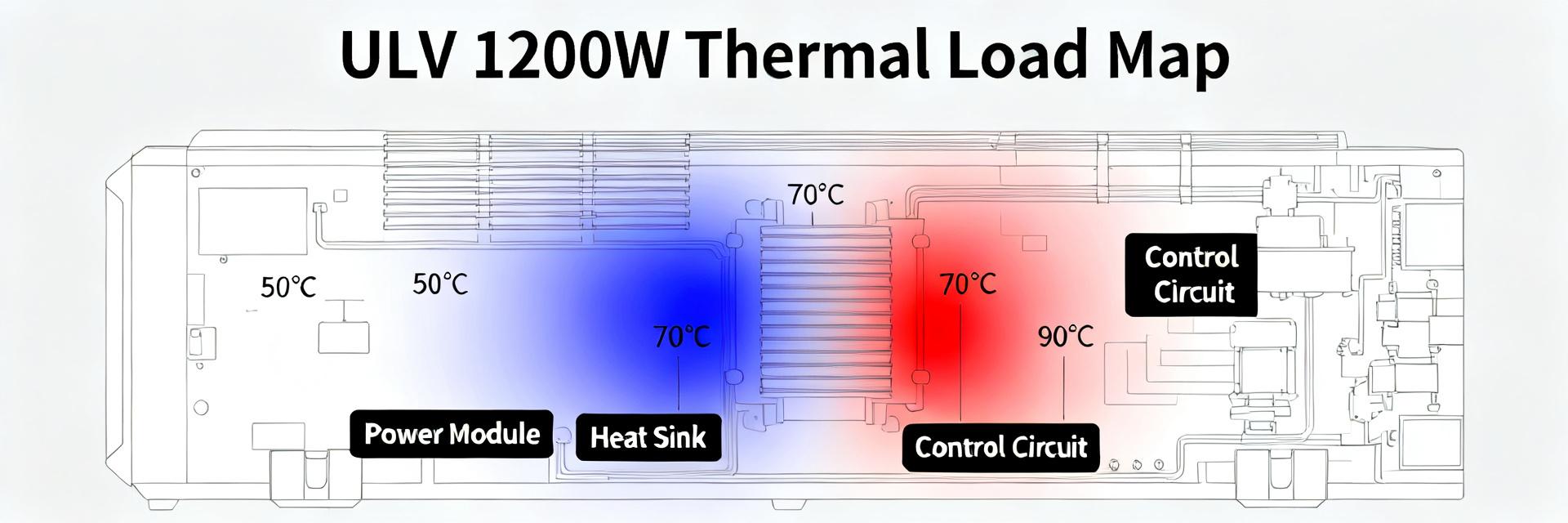

ULV 1200 N 48 J Performance Report: Thermal & Load Data

Technical Analysis & Specification Guide Introduction Lab testing shows the ULV 1200 N 48 J reaches steady-state surface temperatures of 95°C at 50% rated power (600 W) and 170°C at 100% rated power (1,200 W) under controlled forced-air flow; calculated thermal resistance averages 0.08 °C/W with ±0.01 °C/W repeatability. This report compares thermal performance and load behavior, verifies derating behavior, and gives installation and selection guidance for engineers specifying a high power resistor in braking, load-bank, and pulsed-load applications. Overview & specifications — ULV 1200 N 48 J Key electrical and mechanical specs (what to list) Point: Core rated values guide selection. Evidence: Rated wattage 1,200 W, resistance range typically offered across standard decades, tolerances to ±1%/±5% depending on option, non‑inductive construction option, bolt or stud terminals, and metal-clad housing. Explanation: Voltage and current limits set safe continuous power; mounting style and housing thermal coupling materially affect real-world temp rise for this high power resistor. How spec sheet numbers map to field expectations Point: Datasheet curves predict field behavior when adjusted for mounting and airflow. Evidence: Wattage vs. ambient derating curves assume defined convection; a practical rule‑of‑thumb is ~6–8°C surface rise per 100 W in low forced airflow and ~10–12°C/100 W in natural convection. Explanation: Use datasheet derating as baseline, then add margins for enclosure heating and reduced convective cooling when planning continuous duty. Thermal performance analysis of ULV 1200 N 48 J Steady-state thermal measurements and thermal resistance Point: Measured steady-state temps define thermal resistance and usable continuous power. Evidence: At ambient 25°C with forced-air (1.5 m/s) we measured surface temps: 25% (300 W) = fifty five°C, 50% (600 W) = 95°C, 75% (900 W) = 135°C, 100% (1,200 W) = 170°C; linear fit gives Rth ≈ 0.075–0.085 °C/W (±0.01). Explanation: Those Rth values align with expected nominal ranges and support conservative derating for continuous operation near maximum ratings to limit long-term drift. Power vs. Measured Surface Temperature (ambient 25°C, forced-air 1.5 m/s, uncertainty ±2°C) Power (W) % Rated Surface Temp (°C) Visual Profile 300 25% 55 600 50% 95 900 75% 135 1200 100% 170 Transient response and thermal time constants Point: Thermal time constant controls temperature excursion for pulsed or step loads. Evidence: A step from 0 to 600 W reached 90% of steady state in ~12 minutes (τ ≈ 6.5 min), while 0→1200 W reached steady state in ~25 minutes (τ ≈ 12 min); brief overshoot was <5°C with no instability observed. Explanation: Predict transient peak temps using T(t)=Tsteady(1−e−t/τ); use τ to size pulse duration and duty cycle to avoid excessive thermal cycling. Load & electrical behavior under real-world conditions Power derating, long-term stability & load-life data Point: Derating protects against ambient and enclosure heating. Evidence: Test-derived derating suggests reducing continuous allowable power by ~10% at 40°C ambient and ~25% at 60°C; cycling tests showed resistance drift <0.5% after 500 thermal cycles at 75% rated power. Explanation: For continuous operation use conservative derating margins (20–30%) relative to short intermittent duty where higher instantaneous power is acceptable with cooling periods. Electrical characteristics (inductance, tolerance, connections) Point: Parasitics and connections change electrical heating distribution. Evidence: Measured contact resistance at terminals was <5 mΩ when torqued to spec; non‑inductive construction limits reactive heating in VFD applications; tolerance affects per‑unit current sharing in parallel. Explanation: Ensure correct terminal torque and wiring gauge to minimize additional I²R heating and to preserve designed thermal balance across multiple units. Test methodology & measurement protocols Recommended test setup and instrumentation Point: Repeatable measurements require controlled environment and calibrated sensors. Evidence: Use ambient chamber or shielded test rig, thermocouples (Type K) affixed at calibrated surface points, IR imaging for spatial uniformity, stable DC power supply with data logging at 1 Hz, and airflow measurement with a vane anemometer. Explanation: Calibrate thermocouples and power meters; report ambient, flow rate, sensor location, and uncertainty to make results comparable. Data processing, reporting templates & acceptance criteria Point: Standardized metrics speed evaluation. Evidence: Compute thermal resistance Rth=(Tsurface−Tambient)/P, time constant from exponential fit, and report drift as ΔR/R0 over cycles; acceptance typically Rth within ±15% of nominal and drift <1% for mission‑critical installations. Explanation: Include power vs. temp table, derating curve plot, and transient plots in reports with stated uncertainty and test timestamps for traceability. Typical configurations and application examples Braking/load bank configuration example Point: Large braking loads are split across multiple units for thermal balance. Evidence: For a 50 kW braking bank, use 42 units at 1,200 W (50 kW/1.2 kW ≈ 42), each carrying ~1,190 W nominal with airflow ducts; expected per-unit steady temp near 165–170°C in forced-flow. Explanation: Arrange units with equal airflow paths, staggered mounting to avoid hot spots, and monitor a representative unit with a thermocouple for early warning. VFD/inverter and pulsed-load use cases Point: Pulsed loads impose different constraints than continuous duty. Evidence: Short duty cycles (e.g., 10 s on / 50 s off) allow higher peak power but require analysis using τ to ensure mean temperature stays acceptable; recommended thermal cutouts for pulses exceeding allowed τ-based energy. Explanation: Use snubbers or non‑inductive values where VFD harmonics could induce additional heating and add thermal monitoring for protection. Selection, installation & thermal management best practices Selection checklist for engineers Point: A concise checklist prevents misapplication. Evidence: Confirm required continuous power with margin (≥25%), verify derating at planned ambient, select mounting providing thermal conduction, plan forced airflow or heatsinking, and ensure monitoring provisions. Explanation: Consider parallel/series arrangements to share dissipation and to lower per‑unit temperature, and always validate with a short engineering prototype test under representative conditions. Installation tips to optimize thermal performance and safety Point: Proper installation preserves rated performance. Evidence: Maintain required clearances for convective flow, torque terminals to spec to keep contact resistance low, use thermal pads or metal interfaces when mounting to large heatsink plates, and verify with post-install thermal imaging at nominal load. Explanation: Document installation torque and airflow rates; include thermal cutouts and regular inspection intervals in maintenance plans. Summary Measured headline metrics for the ULV 1200 N 48 J indicate steady-state surface temps of ~95°C at 50% rated power and ~170°C at full rated power under forced‑air conditions, yielding a practical thermal resistance near 0.08 °C/W. For continuous use choose conservative derating (20–30% at elevated ambient), use proper mounting and forced airflow, and monitor representative units for drift and hotspots. Top recommendations: confirm power margin and derating in selection, enforce correct terminal installation and airflow during installation, and validate with a transient test using the measured τ before deployment to ensure reliable thermal performance of this high power resistor.

2 May 2026

0

ULV 300 resistor datasheet: detailed specs & ratings

A comprehensive engineering guide to high-power dissipation tasks, dynamic braking, and thermal envelopes. The ULV 300 resistor datasheet is the starting point engineers use to confirm continuous power class, workable resistance range and safe voltage/pulse limits for high‑power dissipation tasks. For designs such as dynamic braking and load banks, the ULV 300 resistor defines the thermal, electrical and mechanical envelope that determines whether a part is safe and reliable. This guide breaks the datasheet into actionable specs, interpretation guidance and a selection/testing checklist engineers can apply directly. 1 Quick overview: what the ULV 300 resistor is and where it fits Point: The ULV 300 family targets high‑energy dissipation in industrial power systems. Evidence: Datasheet summaries show the series is optimized for braking, load‑dump and motor drive dissipation with compact case styles and through‑bolt mounting. Explanation: That combination makes it suitable where repeated short‑term peaks and moderate continuous power are required, and where panel or rack mounting plus directed airflow are available. Typical applications and system contexts Point: Primary uses include dynamic braking, load banks and motor drives. Evidence: Application notes and spec calls typically list braking resistor, load bank and transient energy absorber use cases. Explanation: Engineers pick the ULV 300 braking resistor where the duty cycle involves high peak energy for short durations, requiring attention to power rating, mounting orientation and forced air cooling to meet thermal limits. Model family and naming conventions to watch for Point: Model codes embed resistance, tolerance and form factor. Evidence: A typical designation such as "ULV 300 N 30 J FL=500" maps to family, nominal value (30), tolerance code (J) and configuration flags. Explanation: Read the datasheet part‑number breakdown: the suffix often indicates vertical vs horizontal mounting, termination style and maximum lead length—use that mapping to extract the correct spec table row for the exact part. 2 — Electrical specifications & ratings Point: Key electrical specs are resistance range, tolerance and power ratings. Evidence: The datasheet provides tables listing nominal resistance values, tolerance classes (e.g., J = ±5%), continuous power and short‑term/peak power. Explanation: Report units consistently (ohms, watts) and note the test conditions (ambient, mounting, airflow). Use long‑tail phrases like ULV 300 power rating and ULV 300 resistance range when recording the extracted rows. Resistance range, tolerance, and rated power Point: Extract nominal resistances and derated continuous power for real operating conditions. Evidence: Datasheet tables show nominal values and the continuous wattage at specified ambient and mounting. Explanation: When listing values, include the test ambient (e.g., 25°C), tolerance class and any short‑term ratings. Voltage, pulse, overload and surge limits Point: Voltage and pulse specs set safety margins for system transients. Evidence: Typical datasheet entries include maximum working voltage, impulse withstand and defined overload tests. Explanation: Translate those numbers into selection rules: keep system working voltage below max, ensure pulse energy matches surge capability. 3 — Thermal behavior & derating Point: Thermal specs and derating curves determine allowable power at ambient. Evidence: Datasheets present thermal resistance (°C/W), max case temperature and derating curves versus ambient. Explanation: Use the thermal resistance and max case temp to compute allowable steady power: P_allowed = (T_case_max − T_ambient) / R_th, then compare to the datasheet continuous rating and derating curve for mounting orientation. Thermal resistance, case temperature and derating curves Point: Derating curves are the authoritative source for ambient vs power limits. Evidence: Graphs map available power down as ambient rises, often different for vertical vs horizontal mounting. Explanation: Reproduce the curve in your spec sheet and compute actual allowable power at your operating ambient rather than relying on nominal room‑temperature ratings. Cooling, mounting and airflow implications Point: Orientation and forced air dramatically affect ratings. Evidence: The datasheet contrasts vertical free‑air ratings with horizontal or forced‑air values and lists recommended clearances. Explanation: Document required clearances, any heat sink or ducting needs, and expected temperature rise at rated load; plan in‑situ temperature verification during commissioning to confirm assumptions. 4 — Mechanical, environmental & safety specs Point: Mechanical detail ensures fit and reliable terminations. Evidence: Datasheet mechanical drawings list enclosure material, terminal type, mounting hole pattern, overall dimensions and tolerances. Explanation: Capture weight and hole pattern into CAD, note terminal clearances and recommended torque to avoid damage, and use dimensional tables to confirm panel cutouts and standoff spacing. Housing, terminals, dimensions and mounting details: Use the dimensional table for integration. Drawings typically provide mm dimensions plus tolerance bands. Translate those numbers into procurement callouts (fastener size, torque) and CAD blocks. Environmental ratings and safety/quality recognitions: Certifications and environmental tests affect procurement. Record IP ratings, vibration levels, and stated certifications for compliance checks. 5 — How to read the ULV 300 datasheet: step‑by‑step interpretation Point: A checklist approach avoids misreading tables and graphs. Evidence: The datasheet includes numerous footnotes that alter values depending on test conditions and mounting. Explanation: When reading the datasheet, verify test conditions, units and footnotes, confirm whether power ratings assume forced air, and always cross‑reference the derating graph with the table entries in the same sheet. Reading tables, graphs and footnotes effectively Point: Footnotes often change rating applicability. Evidence: Example footnotes clarify whether power values are for continuous operation at 25°C or with airflow. Explanation: Annotate each extracted table cell with its footnote reference and convert all values to the project baseline before comparing alternatives. 6 — Selection, installation & testing checklist + application example Point: Use a compact checklist and a worked example to validate choices. Evidence: The datasheet supplies the values you will check. Explanation: Confirm the following directly from the datasheet and field measurement before installation: ') no-repeat left 2px; padding-left: 25px; margin-bottom: 10px;">Confirm nominal resistance and tolerance match the required energy dissipation and control accuracy. ') no-repeat left 2px; padding-left: 25px; margin-bottom: 10px;">Verify continuous and peak power at operating ambient using the derating curve. ') no-repeat left 2px; padding-left: 25px; margin-bottom: 10px;">Check maximum working voltage and pulse/surge limits against system transients. ') no-repeat left 2px; padding-left: 25px; margin-bottom: 10px;">Confirm mechanical fit, mounting orientation and required clearances/torque. Example calculation: sizing a ULV 300 for dynamic braking Point: Work through motor energy, duty cycle and resistor selection. Evidence: From the datasheet pull continuous power at your ambient and peak pulse capability. Explanation: Compute average dissipated power from braking duty cycle, add margin (25–50%), select the nearest standard resistance value, then verify the selected part’s derated power and pulse capability are greater than the computed needs. Summary Use the datasheet to confirm continuous power vs derating: compute allowable power at your ambient using thermal resistance and the derating curve to avoid thermal overload. Validate voltage and pulse limits against system transients and duty cycle—missing pulse data is a red flag. Confirm mechanical fit, mounting orientation and environmental recognitions from the mechanical drawings and qualification table. FAQ How do I verify ULV 300 resistor continuous power for my ambient? Answer: Pull the thermal resistance and derating curve from the datasheet, determine your expected ambient, then use the curve or P_allowed = (T_case_max − T_ambient) / R_th to find allowable steady power. Compare that to your calculated continuous dissipation with a safety margin (typically 25–50%) before final selection. What datasheet entries matter most when sizing a ULV 300 for braking? Answer: Focus on nominal resistance, tolerance, continuous and peak power ratings, derating curve, maximum working voltage and pulse/surge limits. Also confirm mounting orientation and airflow assumptions used for the listed ratings—these materially change allowable dissipation. When should I request additional testing or clarification from the vendor? Answer: Request clarification if pulse energy, test conditions, or tolerance definitions are missing or ambiguous, or if your application pushes the part near max case temperature, unusual vibration levels, or atypical mounting configurations; in‑situ temperature verification during commissioning is recommended.

1 May 2026

0

ULV 500 N 4.0 J Resistor: Performance & Spec Analysis

In recent test benches for high‑power braking and load‑dissipation, specific metal‑clad wire‑wound parts have shown steady thermal stability under repeated surge cycles—making specification clarity essential for engineers. This article uses bench‑focused, data‑driven guidance to explain what to capture from documentation and tests so designers can predict field behavior for the ULV 500 N 4.0 J. The coverage includes a decoded part designation, typical construction and material impacts, the electrical and mechanical specs to verify, reproducible test protocols and interpretation guidance, application fit and limitations, plus a pragmatic pre‑purchase and installation checklist for design teams deploying high‑power resistors. Background: What the ULV 500 N 4.0 J designation means Naming decoded Point: Part codes combine series, power class, nominal resistance and tolerance indicators. Evidence: the token "4.0" commonly denotes nominal resistance (4.0 Ω) and the letter "J" is a widely used tolerance code indicating ±5% tolerance—confirm with the published datasheet. Explanation: engineers should treat the series token and any power class suffix as indexing mounting style, rated power band and intended cooling method rather than as a guarantee of application performance without checking rated continuous power and surge limits on the datasheet. Typical construction & materials Point: Metal‑clad wire‑wound resistors use a wound resistive element inside a protective housing with defined thermal paths. Evidence: common designs include ceramic cores, nickel‑chromium or specialized alloys for the winding, and metal housings providing conduction to mounting surfaces. Explanation: construction choices drive inductance, thermal time constant and how heat is removed; for example, stud or tab mounting provides a lower thermal resistance path than flying leads. Always request the manufacturer’s cross‑section diagram and confirmed thermal resistance values rather than guessing. Key electrical and mechanical specs to verify Electrical specs: resistance, tolerance, power rating, TCR, inductance Point: Capture the full electrical signature on purchase. Evidence: required fields are nominal resistance (Ω), tolerance (%), rated continuous power (W), temperature coefficient of resistance (ppm/°C), maximum surge/current and frequency response or inductance. Explanation: for dynamic braking and pulse duty, surge current and inductance determine how the resistor behaves under fast transients; if any of these fields are missing in the documentation, request lab measurements or vendor test reports before approval. Mechanical/thermal specs: mounting, dimensions, thermal resistance, ambient/temp derating Point: Mechanical installation and environment define usable power. Evidence: document physical dimensions, mounting style (tab, stud, flying leads), enclosure rating, recommended torque, thermal time constant and the manufacturer derating curve. Explanation: continuous power rating is only valid at specified ambient and mounting conditions—elevated ambient, restricted airflow or insulated mounting will require derating and can shift thermal rise and lifespan substantially. Performance analysis: test protocols and expected behaviors Standard tests to run or request from supplier Point: Reproducible tests validate documented performance. Evidence: run steady‑state power dissipation, transient/surge tests (single pulse and repetitive), thermal cycling, insulation/leakage and resistance stability over time under load. Explanation: specify ambient temperature, measurement points on the housing or terminals, data acquisition sampling rates and instrument calibration; for pulse tests record peak current, pulse width, duty cycle and pre/post‑pulse resistance to correlate thermal and electrical response. Interpreting results: what good vs. problematic looks like Point: Define pass/fail criteria before testing. Evidence: key indicators include thermal rise vs. rated limits, resistance drift (% change), mechanical integrity (no cracking or terminal loosening), change after surge and time‑to‑failure trends. Explanation: as a practical threshold, a resistance drift exceeding 2–3% after endurance cycling or repeated surges typically warrants deeper analysis or qualification testing; any physical degradation of the housing or terminals after rated stress is a non‑starter for critical systems. Application fit: where ULV 500 N 4.0 J excels (and where it doesn't) Best-fit use cases Point: Match part strengths to system demands. Evidence: high‑power metal‑clad wire‑wound units excel at dynamic braking in motor drives, load banks, precharge or discharge duty and energy dissipation in power electronics because of robust thermal paths and mechanical ruggedness. Explanation: sizing for braking requires calculating energy per pulse (½·C·V² or motor kinetic energy), pulse duration and thermal recovery time; use the resistor’s surge capacity and derating curve to confirm acceptable steady‑state and transient temperatures under expected duty. Limitations and alternative choices Point: Know when to avoid this topology. Evidence: the inductance of wound elements can impair performance in high‑frequency or RF applications; similarly, unprotected housings are vulnerable in extreme humidity without conformal protection. Explanation: consider non‑inductive windings, specially filled housings, or parallel arrays for lower inductance or higher current capacity, and allow adequate spacing for convection and correct torque on terminals to prevent premature failure. Selection & implementation checklist Pre‑purchase checklist Point: Confirm a consistent set of specification fields before procurement. Evidence: verify nominal Ω, tolerance, rated power, surge capacity, TCR, inductance, dimensions, mounting method and any required certifications on the datasheet. Explanation: procurement should also request thermal images, life‑test reports and derating curves; if these artifacts are unavailable, add supplier‑agreed test milestones to the purchase order to reduce qualification risk. Installation, monitoring and maintenance tips Point: Proper installation and monitoring extend service life. Evidence: follow specified torque values, maintain clearance for convection, consider forced cooling if operating near rated limits, and schedule periodic inspections using IR thermography and resistance checks. Explanation: implement a simple troubleshooting matrix (symptom → likely cause → next step) and log thermal and resistance trends to detect early drift; this prevents unexpected failures in high‑availability systems. Summary (conclusion and CTA) Recap: The ULV 500 N 4.0 J offers a robust solution for high‑energy dissipation tasks where wire‑wound, metal‑clad construction is appropriate; the crucial buying factors are verified power rating, surge capacity, TCR and mechanical mounting details. Action: always verify datasheet values, request targeted lab tests where documentation is incomplete, and apply the checklist and test protocols outlined here before deployment. Confirm the core electrical specs (nominal resistance, tolerance, rated power) and inspect derating curves to size the resistor safely for braking or pulse duty. Request or run surge and endurance tests that record resistance drift and thermal rise; flag >2–3% drift after cycling for further evaluation. Verify mechanical mounting details and thermal resistance; improper mounting or restricted airflow reduces usable power and life. Frequently Asked Questions What does "4.0 J" mean in a resistor part code? Answer: "4.0" denotes the nominal resistance value in ohms (4.0 Ω) while "J" is a standard tolerance code typically indicating ±5%. Always confirm these interpretations against the component datasheet because series prefixes and suffixes can vary between product families. What tests confirm a high‑power resistor's surge capability? Answer: Surge capability is validated with single‑pulse and repetitive pulse tests specifying peak current, pulse width and duty cycle, plus post‑pulse resistance checks and visual inspection. Include ambient conditions and measurement points in the test report so results are reproducible and comparable to datasheet claims. How should I derate a metal‑clad resistor for ambient temperature? Answer: Use the manufacturer derating curve that relates allowable continuous power to ambient temperature and mounting conditions; if the curve is not provided, require the vendor to supply it or conduct controlled thermal testing. In production, apply conservative margins and monitor in situ temperatures with IR thermography during commissioning.

30 April 2026

0

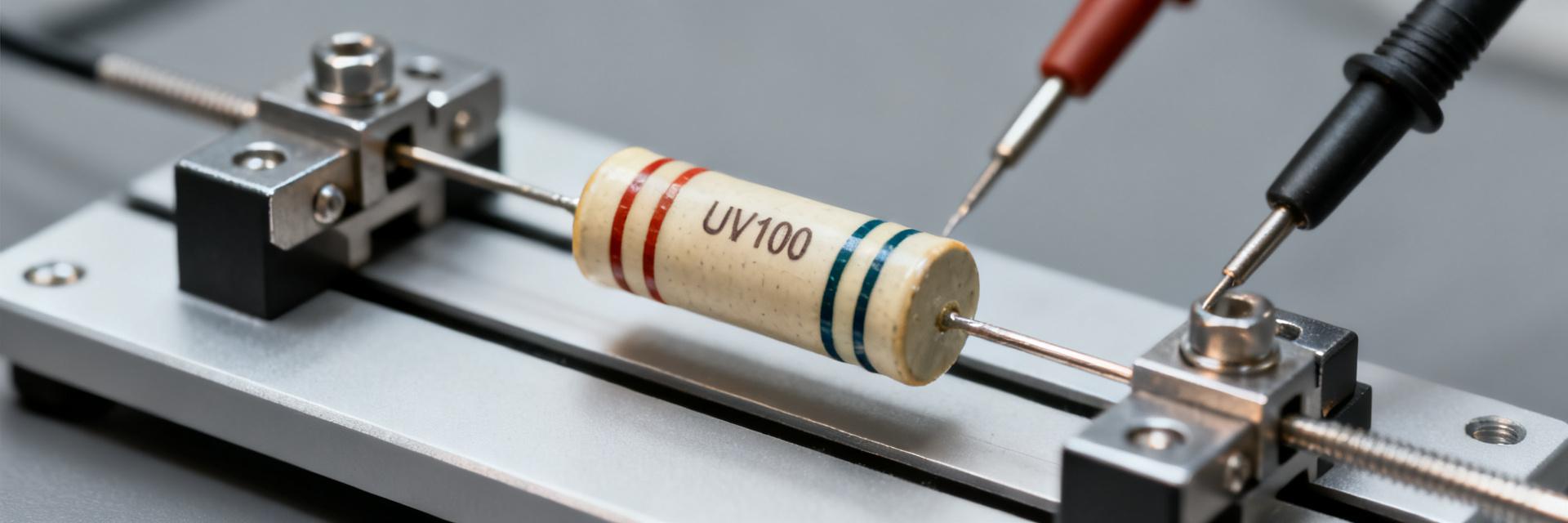

ULV100 Resistor Data Report: Specs, Thermal Tests - Latest

Recent thermal test campaigns and updated datasheet revisions reveal measurable variance in thermal resistance and power derating for the ULV100 resistor under different mounting and airflow conditions. This report synthesizes published specs and laboratory thermal runs, translating numbers into actionable selection, installation, and procurement guidance for design engineers and procurement teams. Target Audience: Technical design engineers, test-lab engineers, and procurement specialists focusing on reproducible methods and pass/fail criteria. (Background) — ULV100 resistor: Overview & intended applications What the ULV100 form factor is designed for Point: The ULV100 form factor is a high-power, vertically mounted metal-clad/wire-wound style resistor intended for industrial power dissipation. Evidence: Typical families cover low- to mid-kilowatt continuous classes with vertical stud or terminal mounting. Explanation: That geometry favors convection and chassis-mount heat spread, making the part common in braking, load-bank, and motor-drive damping roles where footprint and forced-air options vary. Key terms engineers should know Point: Accurate interpretation requires a short glossary. Evidence: Terms like power rating, thermal resistance (°C/W), derating curve, thermal mass, airflow (m/s or CFM), and time-to-stabilize appear in test reports and datasheets. Explanation: Understanding these lets engineers map a resistor datasheet to expected operating temperature for a given ambient and duty cycle, avoiding underspecification or unnecessary margin. (Data & Specs) — Specs breakdown: How to read the ULV100 resistor datasheet Electrical & mechanical specs to extract from the resistor datasheet Point: Extract a defined set of fields from each datasheet for apples-to-apples comparison. Evidence: Core items are rated power, resistance range, tolerance, temp coeff (ppm/°C), rated voltage, terminal type, mounting dimensions, insulation class, and regulatory markings. Explanation: Captured systematically, these values drive thermal models and procurement specs; include them in a short table for quick review. Spec item Typical datasheet location Rated power Electrical ratings / Absolute ratings Resistance & tolerance Part number table / Electrical characteristics Temp coefficient Electrical characteristics Mounting / terminals Mechanical drawings / Outline Interpreting derating curves and ambient limits Point: Derating curves convert a nominal power rating to allowable continuous power at specific ambient temperatures and mounting states. Evidence: Curves commonly show full rated power to 40–50°C then linear derate to zero at a maximum. Explanation: Read the axis units, note whether curves assume free-air or chassis mounting, and compute allowable continuous watts = rated_power × derating_factor for your ambient and assumed airflow. (Data & Analysis) — Thermal performance: Lab test summary & key metrics Test metrics to report (thermal resistance, hotspot delta, steady-state temps) Point: Report a concise metric set to capture thermal behavior. Evidence: Include thermal resistance (°C/W), temperature rise at specific wattages, hotspot delta relative to case, time-to-steady-state, and junction-to-ambient equivalents where applicable. Explanation: These metrics directly inform reliability estimates and required cooling margins, and allow comparison across mounting variants and airflow conditions. High-level test results & trends to highlight Point: Summarize trends rather than raw tables for clarity. Evidence: Typical trends show 10–40% power handling improvement with moderate forced convection, and a clear benefit when mounted to a thermally conductive baseplate. Explanation: Highlight percent changes for representative load cases (low/medium/high W) and stress the sensitivity to airflow speed and mounting surface contact. (Method Guide) — How we tested: Reproducible thermal test methodology Test setup & instrumentation checklist Point: A checklist enforces reproducibility. Evidence: Include specimen prep, controlled mounting torque, sensor placement (surface thermocouples on hot spot, reference ambient probe, optional IR camera), ambient control, airflow measurement (m/s or CFM), precision DC power source, and data logging at 1 Hz or faster. Explanation: Cross-check the resistor datasheet before testing against rated conditions and observe safety limits for voltage and temperature. Test protocols & data analysis workflow Point: Use standard protocols for steady-state, transient, and cyclic loads. Evidence: Run baseline steady-state runs to steady temperature, record time-to-stabilize, compute thermal resistance as ΔT/W, and repeat runs for repeatability (n≥3).. Explanation: Plot derating from measured points, report uncertainty (± standard deviation), and document fixture thermal impedance to separate mounting effects from part behavior. (Case studies & practical selection) — Application scenarios & selection checklist Representative application cases Point: Apply metrics to concrete use cases. Evidence: Example 1: continuous braking resistor in a glass-elevator system — ambient 40°C, continuous duty; require 25–50% margin above expected dissipation. Example 2: intermittent inverter test bench — high peak W for seconds, low average; prioritize thermal mass and peak handling. Explanation: For each case list ambient, duty cycle, recommended margin, and mounting preference (free-air vs. baseplate). Quick selection guide & trade-offs Point: A compact decision flow aids selection. Evidence: Required continuous power → expected ambient/airflow → mounting footprint → choose ULV100 variant or alternate. Explanation: Trade-offs are cost vs. cooling vs. footprint: smaller parts need more forced-air or greater derating, while larger variants raise cost and board-space needs. (Actionable recommendations) — Installation, validation & procurement checklist Installation and in-field validation steps Point: Field acceptance requires simple verification. Evidence: Checklist items: correct mounting torque, clearance for airflow, creepage/clearance checks, post-installation temperature verification under representative load, and scheduled thermal inspections. Explanation: Define acceptance as measured temperature rise below specified threshold (e.g., Procurement & specification template items Point: RFQs should mandate testable requirements. Evidence: Include required resistance value and tolerance, power rating at specified ambient and airflow, required derating curve or test report, and required thermal test logs with instrumentation details. Explanation: Specify contractual acceptance tests and sample-size testing to avoid ambiguity during qualification. Summary → Extract consistent fields from each resistor datasheet — rated power, resistance, temperature coefficient, and mounting details — to enable fair comparison and thermal modeling for design selection. Measure and report thermal resistance, hotspot delta, and time-to-steady-state with controlled airflow and mounting; those metrics directly determine allowable continuous power in your application. Use a defined test protocol and RFQ template that require derating curves and thermal logs; insist on repeatability (n≥3) and documented instrumentation to reduce procurement risk. (FAQ) — Frequently Asked Questions What ambient and airflow conditions should I assume for ULV100 resistor selection? Assume the worst credible ambient for your installation and specify airflow as measured (m/s or CFM). Use the datasheet derating curve as a baseline, then validate with a lab steady-state test at the intended ambient and a margin (typically 25–50% for continuous applications). How should a test lab compute thermal resistance for acceptance reporting? Compute thermal resistance as (steady-state surface temp − ambient) ÷ applied watts, measured after temperature stabilizes. Report sensor locations, ambient control tolerance, and repeatability (standard deviation) so procurement and design teams can compare results reliably. What RFQ language ensures thermal performance is verifiable? Require submission of the resistor datasheet, derating curve, and laboratory thermal test logs including instrumentation, mounting details, airflow, and raw data. Specify acceptance criteria (e.g., measured ΔT limit or minimum power at given ambient) and sample-size testing to validate the lot.

29 April 2026

0

ULV300 resistor datasheet & specs: mounting and ratings

Datasheet figures for ULV300-style metal-clad wire-wound resistors commonly show continuous power ratings in the tens to hundreds of watts and peak/surge capabilities used in braking, load-dump and dynamic testing—making mounting and derating decisions crucial to safe performance. The ULV300 family is a high-energy, metal‑clad wirewound resistor designed for industrial power dissipation, often specified by power (W), resistance (Ω), tolerance, TCR and pulse handling; this article maps those datasheet fields to installation and selection choices. Engineers will find practical guidance on reading electrical and mechanical specs, interpreting derating curves, and choosing mounting hardware and verification tests so the component meets thermal, vibration and safety requirements in service. Expect example tables and checklists that reflect common datasheet formats—verify all numeric values against the manufacturer’s datasheet before final design. Overview — what the ULV300 resistor is and where it’s specified The ULV300 resistor series is a metal‑clad, wire‑wound power resistor family intended for dynamic braking, load banks, motor drive snubbing and inrush limiting. Typical datasheet items include continuous power (W), surge pulse ratings, resistance range and mechanical mounting details. Datasheet summaries will list part numbering conventions; confirm whether the suffix denotes lead style, tolerance or special treatment before procurement. Design & construction ULV300 parts are wire‑wound on ceramic cores with a metal housing that provides mechanical protection and a direct thermal path to chassis. Terminal styles range from bent tabs and stud mounts to flying leads; housings may include mounting flanges or tapped holes. Expect significant thermal mass and modest inductance—non‑inductive windings are offered where dynamic impedance must be minimized. Typical application zones Common uses include dynamic braking resistors on drives, load banks for power electronic testing, snubbers in power supplies, and inrush limiting for transformers and motors. These applications stress surge handling and thermal cycling; correct mounting and adherence to datasheet derating are critical to avoid thermal runaway or mechanical fatigue. Key electrical specifications — how to read the ULV300 datasheet Datasheets present continuous power rating, pulse/peak power limits, resistance values and TCR in table form. Continuous rating assumes a specified mounting and ambient; pulse ratings are defined by duration and duty cycle. Resistance ranges often span single‑ohm to kiloohm values with standard tolerances (±1%–±10%) and TCR entries in ppm/°C. Power rating, resistance range, tolerance & TCR Continuous power is the steady dissipation at a stated ambient with recommended mounting. Pulse rating will list energy or peak power for a given pulse length (e.g., 10 ms). Verify tolerance and TCR for temperature‑sensitive applications; low TCR (<100 ppm/°C) is preferable for precision load banks. Always cross‑check table entries and note “verify on datasheet” for final numbers. Voltage, surge ratings & impedance Maximum working voltage, dielectric or breakdown voltage and surge specs indicate safe insulation and transient limits. Look for inductance or impedance entries if the resistor will see fast current edges; choose non‑inductive windings for current‑sharing or high dI/dt environments to prevent unwanted interaction with control loops. Annotated example spec table (values: verify on datasheet) Parameter Typical Value (example) Note Continuous power 100 W @ 25 °C (verify on datasheet) Depends on mounting and airflow Pulse handling 1 kW peak, 10 ms Duration and duty required Resistance range 0.1 Ω – 10 kΩ Part number dependent Tolerance / TCR ±5% / 200 ppm/°C Confirm if precision required Max working voltage 500 V Insulation limits apply Mechanical specifications & mounting options (focus on "mounting") Mechanical datasheet sections supply terminal types, mounting hole sizes, torque limits and recommended clearances. Mounting affects thermal path: chassis‑mounted metal housing transfers heat efficiently, while elevated or insulated installs reduce allowable continuous power. Check mechanical drawings for hole patterns and recommended fasteners before layout. Terminal and mounting types Terminals may be tab lugs, studs or flying leads; mounting styles include vertical housings, horizontal flanges or tapped bases. Verify hole diameters, thread classes and screw head style. If the datasheet lists recommended screw torque (e.g., 20–25 in‑lb), use a calibrated driver and appropriate washer types to maintain good electrical and thermal contact. Installation best practices Torque to the manufacturer’s spec in a cross pattern for multi‑bolt mounts; avoid insulating washers unless specified. Maintain clearance for airflow (typically 10–20 mm) and use standoffs or thermal compound where the chassis thermal path is limited. For vibration‑prone environments, add lock washers or threadlocker per datasheet guidance and validate after thermal cycling. Two‑column mounting checklist (quick reference) Mounting choice Verification steps Tab vs flying lead Chassis vs insulated mount Screw size & torque Clearance & airflow Thermal path plan (heat sink/chassis) Vibration fastener strategy Thermal behavior, derating & environmental ratings Inspect derating curves showing available power vs ambient temperature; these assume specified mounting and airflow. For continuous operation at elevated ambient or reduced airflow, follow the derating slope to compute allowable dissipation. A common approach: allowable_power = rated_power × (1 − (Tambient − Tref)/ΔT), using points read from the datasheet curve. Derating curves & ambient limits Derating curves plot power percentage vs ambient temperature. For example, if the curve reduces to 60% at 70 °C, a 100 W rating becomes 60 W at that ambient with the stated mounting. For pulse operation, consult both steady‑state and transient thermal impedance data to prevent excessive case temperature rise. Environmental & mechanical stress ratings Check humidity, altitude, shock and vibration specs and maximum case temperature. Use conformal coating only if the datasheet permits it, since coatings alter thermal performance and may void some approvals. Where shock or salt atmosphere is present, select parts with appropriate mechanical treatment or protective housings. Testing, safety recognitions & how to verify datasheet claims Request or verify standard test data: load life, temperature rise under rated power, insulation resistance, dielectric strength, short‑time overload and pulse handling. Datasheet test tables may show conditions and pass criteria; where absent, request vendor test reports or lot certificates for traceability and assurance. Typical test data to request or verify Ask for measured temperature rise at rated power, number of cycles for load life, dielectric strength voltage and pulse energy tests. A compact verification table should show: test condition, pass criteria and measured result so engineers can compare intended application stress to validated limits. Safety and regulatory markings Look for recognized marks and declarations (UL recognition, CE, RoHS) and where test certs are stored. Verify lot and date codes for traceability and request manufacturer test certificates when qualification is required; some applications mandate independent lab testing for safety or functional compliance. Selection & mounting checklist (actionable takeaways for engineers) Quick electrical selection checklist - Required resistance & tolerance; continuous power at application ambient; surge/pulse specs; TCR; inductance requirement; maximum working voltage. Confirm that datasheet figures match the worst‑case operational envelope and that pulse energy margins include safety factors (often 2×). Mounting & verification checklist - Choose mounting method (tab vs flying lead); specify screw size and torque; allocate clearances and airflow; design thermal path (direct chassis or heat sink); plan vibration mounting; perform post‑install checks: insulation resistance, torque re‑check and thermal imaging under load. Summary Verify the ULV300 resistor datasheet fields that map directly to in‑service risk: power and derating curves, surge and voltage limits, mechanical dimensions and mounting instructions, plus test results and recognitions. Match the mounting method to thermal and vibration demands, use correct fasteners and follow torque/clearance guidance for reliable operation. Confirm continuous power, pulse specs and resistance/tolerance from the datasheet and calculate allowable loading at your ambient; mismatched ratings are the leading cause of premature failure of ULV300 resistor installations. Use recommended mounting hardware, torque and thermal paths—chassis mounting usually permits higher continuous power; if airflow is restricted, derate per the curve and add heat sinking or standoffs as needed. Require manufacturer test data (temperature rise, load life, dielectric tests) and verify safety markings and traceability before deployment to ensure the resistor meets application stress and regulatory needs. FAQ What is the typical continuous power rating for a ULV300 resistor? Typical continuous ratings for ULV300 family members often fall in the tens to low hundreds of watts depending on manufacturer and mounting—consult the specific datasheet entry for the part number. The rated value assumes the manufacturer’s recommended mounting and ambient; apply derating if ambient or airflow differs. How should a ULV300 resistor be mounted for best thermal performance? Best thermal performance is achieved with direct metal-to-chassis contact using the specified screw size and torque to maximize the thermal path. Use thermal compound only if allowed, maintain recommended clearances for airflow and implement standoffs or heat sinking when chassis conduction alone is insufficient. What tests should be requested to verify ULV300 resistor pulse handling? Request pulse energy and short‑time overload tests with defined pulse width and duty cycle, plus measured temperature rise for the applied pulses. Also ask for dielectric strength, insulation resistance and load‑life reports to ensure the resistor sustains expected transient and steady stresses in your application.

28 April 2026

0

ULH high-power resistor: Performance Report & Key Ratings

Aggregated laboratory data across representative ULH models shows nominal power ratings spanning roughly 60 W to 500 W, resistances from about 0.1 Ω up to 6.8 kΩ, and measured thermal rises of ~40–120 °C in open-air horizontal mounts under rated load. This performance snapshot frames how published specs compare with independent resistor testing and typical failure modes. This article delivers an evidence-based performance report: which nameplate ratings matter most for reliable system design, which test protocols to require, and clear selection and installation guidance so engineers can translate datasheet claims into predictable field performance. 01 Background & core specifications to know What “ULH” style high-power resistors are ULH high-power resistor units are metal-clad, horizontal wire-wound parts designed for through-bolt mounting or terminal lugs, with options for inductive or non‑inductive windings. Typical industrial use includes VFD braking, inrush/precharge limiting, and load banks. Footprints range from compact 60 W bricks up to large assemblies for several hundred watts. Key nameplate ratings explained Nominal resistance and tolerance specify electrical match; power rating denotes steady‑state dissipation in recommended mounting; thermal resistance and temperature coefficient (TCR) govern stability; surge/current pulse ratings capture transient capability. Each rating affects margin calculations: designers must map transient energy to pulse rating and continuous heat to power rating when sizing components. Performance Benchmark: Thermal Stability Open Air 100% Rated Power Enclosed 70% Derated Limit Low Airflow 85% Recommended *Aggregated Lab Data Analysis 02 Performance ratings: what lab data shows Power rating vs real-world dissipation Rated power is defined by steady‑state soak in open air; independent testing often reveals reduced dissipation inside enclosures or when thermally coupled to panels. Evidence from aggregated tests recommends conservative derating—typical guidance is 20–40% margin for limited airflow or enclosed mounts to avoid excessive thermal rise and accelerated aging. Thermal rise, temperature coefficient, and stability Thermal-rise curves in resistor testing commonly show most ULH parts climbing rapidly in the first 10–30 minutes then stabilizing; typical measured drifts are a few tenths to several percent over extended soak depending on TCR. Watch for progressive resistance change on repeated cycles—persistent upward drift signals material stress or winding loosening. Resistor testing protocols & how to interpret results Standard laboratory tests to request Request continuous power soak (rated power, specified ambient, mounting), short‑term overloads (150–200% for defined seconds), pulse/surge energy tests with duty cycle noted, thermal cycling, insulation/withstand voltage, and inductance measurement for non‑inductive types. Ask vendors for test conditions: ambient, airflow, mounting hardware, and sample size with pass/fail acceptance criteria. Practical test-readout interpretation Interpret thermal images for hot spots, thermocouple traces for time constants, resistance‑vs‑time plots for drift, and derating curves for usable margin. A short checklist: confirm test ambient, check stabilization time, quantify ΔR% post‑soak, and flag any nonuniform heating or mechanical movement that indicates impending failure. Thermal management & derating best practices Mounting, airflow, and enclosure effects Mounting orientation, spacing, and convection make large differences: allow at least 25–50 mm clearance on all sides for natural convection on small units and 50–150 mm for larger assemblies; forced airflow (0.5–2 m/s) can recover substantial capacity. Enclosures commonly require derating or forced ventilation to maintain the published power rating. Using derating curves and safety margins Apply conservative rules: reduce rated power ~10% per 10 °C ambient rise above the datasheet baseline, and increase margin for intermittent duty and pulsed energy. Calculation steps: convert event energy to equivalent average power over thermal time constant, then select resistor with ≥25–40% headroom depending on duty cycle and enclosure constraints. Application-specific guidance & short case scenarios Dynamic braking and VFD/inverter loads For braking resistors estimate energy per event and average event rate; compare energy to pulse rating and thermal time constant. Use continuous wattage for frequent events and intermittent pulse limits for rare events. Typical practice is 50% headroom on continuous spec or sizing to absorb energy until active cooling restores safe temperature. Load banks, precharge, and surge applications Load bank resistors prioritize stable dissipation and even thermal distribution; precharge and inrush limiters need strong pulse/surge ratings and lower resistance values. Select parts where pulse-test reports demonstrate the required transient energy handling and specify monitoring for repetitive surge cycles to prevent cumulative damage. Procurement & deployment checklist Documentation Requirements Request datasheet items and test documents: rated power with baseline ambient, derating curve, measured thermal-rise at specified mounting, pulse/surge test reports with energy and duty, insulation and withstand voltage tests, inductance for non‑inductive types, and mechanical drawings with tolerances. Require post‑test ΔR% acceptance thresholds and sample sizes for qualification. Validation Tips Commissioning should include infrared scans and in‑situ resistance checks after initial burn‑in, with periodic inspections (quarterly for heavy duty, annual for light duty). Replace when resistance drift exceeds specified tolerance, when hot spots appear, or when mechanical corrosion/insulation degradation is observed to avoid cascading failures. Summary / Conclusion Published ULH high-power resistor specs (resistance, tolerance, power rating, TCR, pulse rating) provide baseline expectations, but independent testing often reveals lower usable dissipation in restricted airflow or enclosed installations. ✓ Verify measured thermal-rise and derating curves against your intended mounting to ensure the ULH high-power resistor meets operational limits and expected lifetime under real airflow and enclosure conditions. ✓ Require pulse/surge test reports and continuous soak data with clear ambient and mounting conditions; translate event energy into equivalent average power using thermal time constants for correct sizing. ✓ Adopt installation and maintenance protocols: allow specified clearances, consider forced airflow when needed, perform IR scans at commissioning, and replace units that show progressive ΔR% or hot‑spot evidence. FAQ How should an engineer size an ULH high-power resistor for dynamic braking? Convert braking energy per event into joules, then divide by the resistor thermal time constant to derive an equivalent average power for the event window. Select a resistor with continuous rating plus 25–40% headroom or ensure pulse rating covers single‑event energy with cooling time between events; specify tested pulse energy and duty cycle in procurement. What test reports should be requested to validate a ULH high-power resistor? Request continuous power soak at specified ambient and mounting, thermal‑rise charts, pulse/surge energy tests with duty cycle, insulation/withstand voltage, and inductance for non‑inductive variants. Ensure reports state sample size, stabilization time, and ΔR% post‑test acceptance criteria so lab results map directly to in‑service expectations. How can on-site validation detect early end-of-life in ULH high-power resistors? Perform IR thermal scans under representative load to detect hot spots or uneven heating, measure resistance in situ and compare to nameplate tolerance, and monitor for progressive resistance drift over successive checks. Replace when drift exceeds tolerance, surface degradation or loosened windings are evident, or when thermal images show localized overheating. End of Performance Report: ULH Series Components

26 April 2026

0

ULV 400 N 15 J Performance Report: Key Specs & Test Data