-

- 联系我们

- 隐私政策

- 条款 和 条件

- Cookies 政策

4310R-101-104阻网络:完整的规格和测试的数据

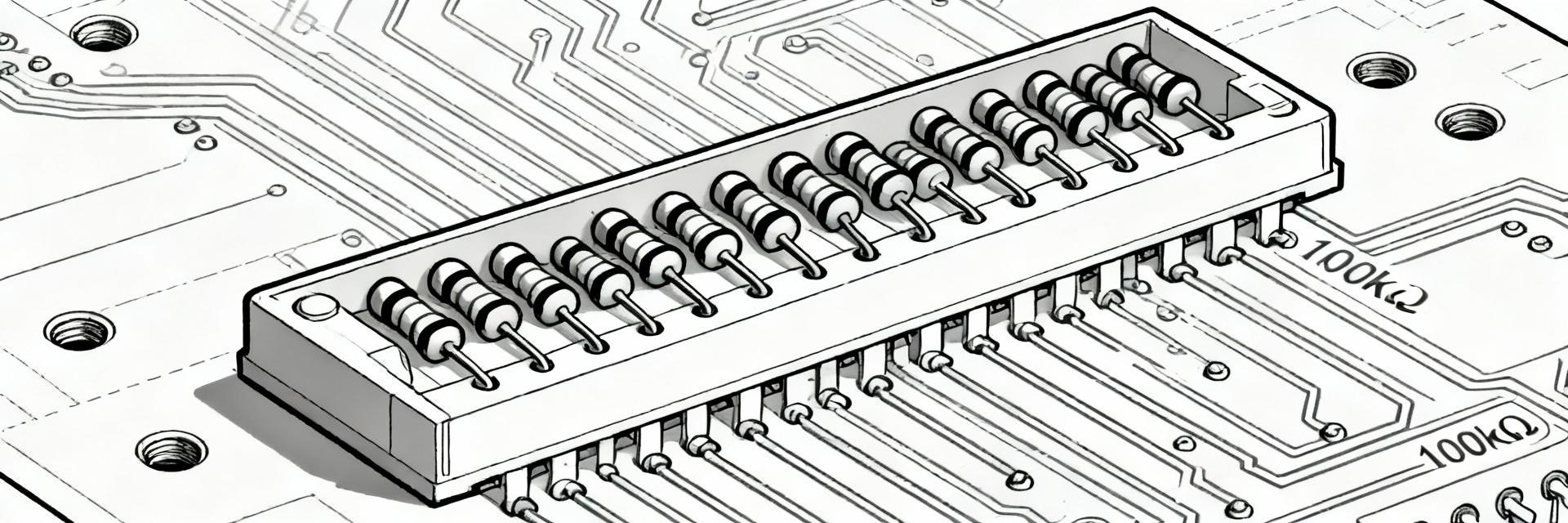

数据手册和实验台测量显示,4310R-101-104是一个9电阻、10针母线SIP电阻网络,标称元件为100 kΩ,容差2%,TCR±100 ppm/°C,总耗散约1.25瓦——非常适合紧凑的上拉/下拉阵列和匹配偏置网络。本文提供完整的规格、可重复的测试方法、具代表性的测量结果以及工程验证的实用设计/替代指导。

产品背景与核心规格(背景介绍)

主要电气规格

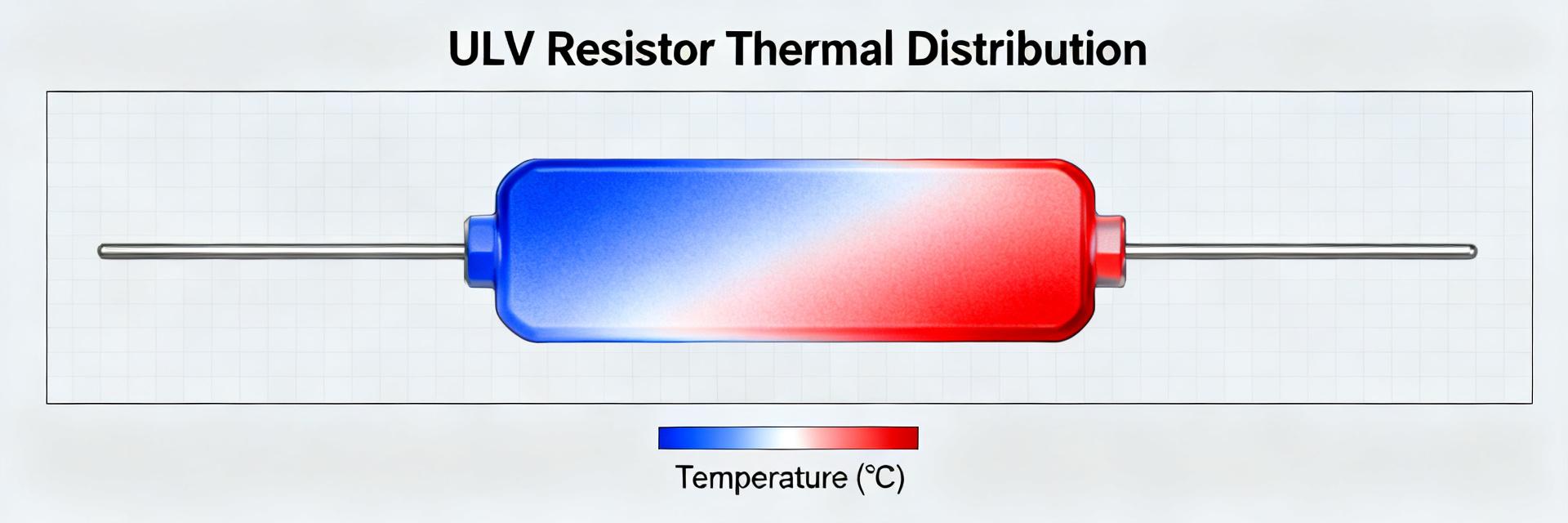

标称电阻:每个元件100 kΩ;公差:2%(标准)。元件:总线SIP中的9个电阻,总引脚:10。TCR指定为±100 ppm/°C(厚膜规格,在定义的温度间隔内测量)。功率:每个元件≤200 mW(按温度降额),总网络耗散≤1.25 W。工作温度范围通常为−55°C至+125°C。使用下面的规格表进行紧凑参考,并在生产前验证特定批次数据。

| 参数 | 值 |

|---|---|

| 配置 | 9× resistors, bussed SIP (10 pins) |

| 电阻(标称) | 100 kΩ |

| 宽容 | ±2% |

| TCR | ±100 ppm/°C |

| 每元素功率 | ≤200 mW |

| 总耗散 | ≈1.25 W |

| 工作温度 | −55 °C 至 +125 °C |

| 包装 | 模塑SIP,总线连接;符合RoHS标准 |

机械和引脚要领

引脚编号:10个引脚,中心公共(总线)加上9个单独的电阻器引脚。通孔SIP的典型主体长度很紧凑——请查看数据表以了解确切的占地面积和公差。处理:通孔引线接受标准焊角;在波峰焊过程中避免过多的回流热。下面是一个简单的ASCII引脚图,说明了PCB的总线/常见布置,以供参考。

Pin1 Pin2 Pin3 Pin4 Pin5 o-----o-----o-----o-----o测试台方法与测量电气性能(数据分析)

测试设置和测量程序

推荐设备:4½位万用表、LCR表、恒温箱、稳压直流电源、数据记录仪和强制空气进行热测试。在三个环境点(例如,25°C、85°C、-40°C)进行测量,每个点浸泡5-10分钟。对于TCR使用电阻随温度扫描;对于功率降额,对每个元件逐级增加电压/电流,同时监测温度上升和电阻变化。使用n≥10个单元进行基本统计置信度。

测量结果与解释

报告平均阻力、标准偏差、最小/最大范围和相对于温度和功率的百分比变化。示例样本表格(代表性):

| 公制 | 测量 |

|---|---|

| 平均R(25°C) | 100.2 kΩ |

| 标准差(n=10) | 0.9 kΩ (≈0.9%) |

| TCR(斜率) | ≈+95 ppm/°C |

| ΔR @ 200 mW elem | +0.6% after 30 s |

解释:总线元素之间的比率稳定性通常比绝对漂移更好;当相邻电阻耗散功率时,注意开路元素和热相互作用。绘制电阻与温度的关系以及%变化与施加功率的关系,以获得清晰的通过/失败标准。

应用与设计注意事项(方法指南)

Where to use this resistor network

常见用途:用于多IO总线的上拉/下拉电阻,用于参考和偏置网络的匹配阵列,以及用于逻辑线的无源电阻总成。相比分立元件的优势包括节省电路板空间、匹配的热行为和减少组装时间。示例电路:(1) MCU IO总线上拉阵列,(2) 8通道分压器为多输入比较器提供共享公共节点。

尺寸、降额和PCB布局提示

计算元件功率: P=每个电阻器的V²/R。根据数据表,线性降低70°C以上的功率,以保持每个元件低于200毫瓦。保持引线周围的PCB铜以进行热扩散,在SIP下谨慎使用热通孔,并在大功率相邻电阻器之间留有间隙以减少热耦合。清单:验证每个元件的功率、倒铜量、通孔位置和焊点尺寸。

替换和兼容性清单(案例研究风格)

何时选择替代或升级

如果需要更严格的容忍度,请考虑替换(

Spec matching checklist for safe substitution

Printable checklist: match resistance value per element, tolerance, TCR, number of resistors/pinout, power per element and total, package footprint and environmental ratings (temp/humidity). Verify mechanical fit, derating curves and expected ratio stability before committing to a cross.

Custom styled list to control marker appearance (adjusted ::marker equivalent)- Resistance and tolerance match

- TCR and derating behavior

- 引脚和封装兼容性

- 每个元件的功率和总耗散

- 环境和焊接等级

实用测试清单和样品实验室报告(行动建议)

逐步测试清单

1) Visual and continuity inspection; 2) Initial cold resistance at 25°C for all elements; 3) TCR sweep (−40 → +85°C or wider) with soak and record; 4) Power/thermal test: apply stepwise power to single element up to derated limit; 5) Post‑stress resistance check and humidity/aging if required. Include ESD and safety precautions when handling and powering networks.

Sample lab report template & recommended data presentation

Report sections: Summary, Equipment, Test Conditions, Raw Data, Plots (resistance histogram, R vs T, %Δ vs power), Pass/Fail and Recommendations. Example conclusion language: “Units conform to datasheet specs for resistance, TCR and power derating under tested conditions; no open elements or unacceptable drift observed.”

Key summary

- The 4310R-101-104 is a compact 9‑resistor, 10‑pin bussed SIP resistor network with 100 kΩ elements and 2% tolerance; validate per‑element power and TCR during qualification.

- 台架测试应包括电阻分布、TCR扫描和功率降额,n≥10个单位;将结果显示为平均值/标准差、R vs T和%变化vs功率图。

- 使用替代检查表匹配电阻、公差、TCR、引脚和功率;注意热耦合和PCB铜以确保可靠运行。

常见问题

手风琴常见问题解答,使用细节/摘要(原生、语义、有利于SEO)如何在我的实验室中验证4310R-101-104 TCR?

What are typical failure modes for this resistor network?

Can I use the 4310R-101-104 for high‑voltage applications?

-

SI3402-B-GMRSILICON LABS(芯科)

SI3402-B-GMRSILICON LABS(芯科) -

EFM8BB21F16G-C-QFN20RSILICON LABS(芯科)

EFM8BB21F16G-C-QFN20RSILICON LABS(芯科) -

CP2102N-A02-GQFN20RSILICON LABS(芯科)

CP2102N-A02-GQFN20RSILICON LABS(芯科) -

SI53307-B-GMRSILICON LABS(芯科)

SI53307-B-GMRSILICON LABS(芯科) -

SI53361-B-GMRSILICON LABS(芯科)

SI53361-B-GMRSILICON LABS(芯科) -

SI53340-B-GMSILICON LABS(芯科)

SI53340-B-GMSILICON LABS(芯科) -

SI53306-B-GMRSILICON LABS(芯科)

SI53306-B-GMRSILICON LABS(芯科) -

C8051F300-GMRSILICON LABS(芯科)

C8051F300-GMRSILICON LABS(芯科) -

SI4464-B1B-FMRSILICON LABS(芯科)

SI4464-B1B-FMRSILICON LABS(芯科) -

SI5351A-B-GTRSILICON LABS(芯科)

SI5351A-B-GTRSILICON LABS(芯科)