-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

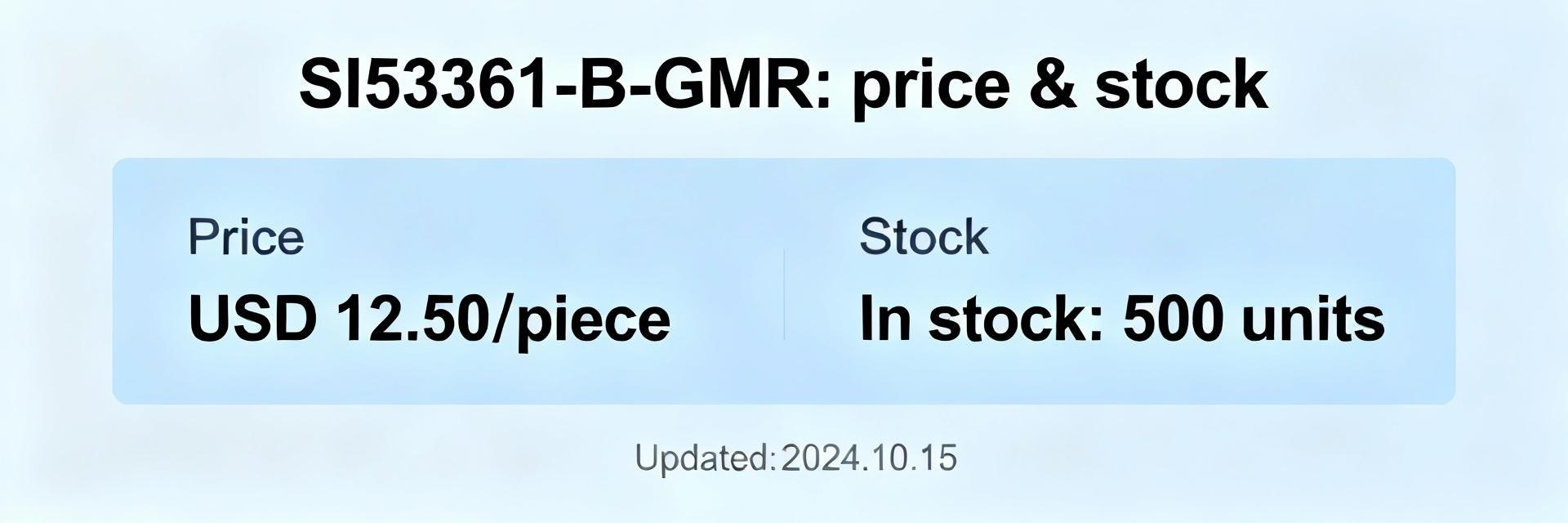

SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

As of writing (current distributor snapshots), SI53361-B-GMR shows broad availability across major US distributors with typical unit prices ranging from about $2.49 to $3.50 — making it a cost-effective option for clock distribution in many designs. This data-driven overview dives into the SI53361-B-GMR specs, current stock trends, and practical buying guidance so engineers and buyers can decide quickly and confidently.

Point: The following guide synthesizes distributor listings, vendor datasheet highlights, and bench-practice recommendations to give US-based procurement and engineering teams a concise, actionable view. Evidence: distributor inventory listings (Digi‑Key, Mouser, Arrow, Win‑Source, UTmel) and vendor product pages inform the stock and package details cited below. Explanation: readers should use the checklist and test-plan here alongside timestamped distributor snapshots for procurement records and lifecycle checks.

1 — Product Background: What the SI53361-B-GMR Is and Where It Fits

Key function and target applications

Point: The SI53361-B-GMR is a compact 2:8 clock buffer/multiplexer (clock fanout) designed for low jitter and low skew board-level distribution. Evidence: vendor part descriptions and family documentation describe a small-footprint 16‑VFQFN package with exposed pad and typical operating frequencies up to 200 MHz. Explanation: this combination—multiple buffered outputs, low timing error, and a thermally enhanced VFQFN package—makes the device suitable for networking, telecom, storage controllers, and FPGA/SoC clocking where deterministic timing and small BOM cost are priorities.

Manufacturer history & part family context

Point: The SI53361 sits within the Si5336x family lineage and is offered under Silicon Labs / Skyworks Solutions branding in distribution channels. Evidence: product pages and cross-references at major distributors show both Silicon Labs and Skyworks listings for Si53361 variants. Explanation: compared with other Si5336x parts the SI53361 variant focuses on a 2-input, eight-output topology with a particular power profile and package choice; designers should compare channel count, input mux flexibility and programmable features across the family when choosing alternatives.

Compliance, thermal & lifecycle considerations

Point: Compliance flags, thermal-pad practices and lifecycle status checks are essential before committing to production. Evidence: distributor product pages and the vendor datasheet indicate RoHS/lead‑free flags and standard ESD notices; the exposed‑pad VFQFN requires recommended soldering and via patterns for thermal dissipation. Explanation: designers should confirm RoHS and ESD protection statements on the distributor page, follow recommended exposed‑pad soldering and thermal via arrays on the PCB, and validate part lifecycle (active vs last‑time‑buy risk) via the manufacturer's product status table before volume buys.

2 — SI53361-B-GMR Technical Specs: Pinout, Electrical & Timing (Specs)

Electrical characteristics & recommended operating conditions

Point: Typical operating conditions center on a 3.3 V supply and LVCMOS logic levels; decoupling and VCC sequencing guidance reduces risk. Evidence: datasheet summaries and distributor specification snippets identify 3.3 V nominal operation, LVCMOS outputs and recommended decoupling near power pins. Explanation: follow standard practice—place 0.1 µF ceramic decouplers at each VCC pin plus a bulk 1–10 µF on the board, sequence supplies per datasheet notes, and avoid exceeding absolute maximums shown in the thermal/electrical tables to prevent damage. For exact current consumption and worst‑case figures consult the datasheet for idle vs toggling current in your output loading scenario.

Timing performance: jitter, skew, and propagation delay

Point: The SI53361-B-GMR emphasizes low jitter and tight output-to-output skew to simplify system timing budgets. Evidence: vendor timing tables report low RMS jitter (device-config and measurement‑method dependent) and skew values suited to board‑level fanout. Explanation: interpret vendor jitter figures as device contribution; design-level jitter budgets must include source PLL jitter, board crosstalk, and measurement setup. Measure timing with high‑bandwidth instruments, and treat vendor numbers as the starting point for margin calculations.

Pinout, package and layout guidance

Point: Correct footprint, exposed pad soldering and routing strategy materially affect thermal and electrical performance. Evidence: the 16‑VFQFN package map highlights critical pins (inputs, outputs, OE, VCC, GND, EP) and board‑layout notes in vendor documents. Explanation: implement a ground plane under the device, add thermal vias in the exposed pad area (staggered to ease solder wicking), route high‑speed clock outputs with controlled impedance and matched lengths where required, and include accessible test points for critical clocks to simplify lab validation and in‑line testing.

3 — SI53361-B-GMR Stock & Price Analysis: Current Distributor Data (Stock)

Snapshot of distributor availability & price range

Point: Distributor snapshots at the time of this writing show widespread availability and a unit‑price band near $2.49–$3.50. Evidence: listings at major US distributors (Digi‑Key, Mouser, Arrow) and specialized resellers (Win‑Source, UTmel) report stock or obtainable lead‑times with unit pricing in the stated range. Explanation: for procurement, capture timestamped screenshots or API pulls of these listings to document price/availability at order time and include transaction references in the purchase order for traceability.

| Distributor | Availability | MOQ | Typical Unit Price | Lead Time |

|---|---|---|---|---|

| Digi‑Key | In stock (varies) | 1 | $2.49–$3.10 | Immediate where shown |

| Mouser | In stock / limited | 1 | $2.75–$3.30 | Immediate or short |

| Arrow | Stock / alternative sourcing | 1–10 | $2.60–$3.50 | Varies |

| Specialized resellers | Available (check authenticity) | Varies | $2.50–$4.00 | Check seller |

Trend analysis & lead-time signals

Point: Short-term replenishment, quoted long lead times, and price movements give signals for buying strategy. Evidence: repeated snapshot comparisons and distributor lead‑time notes indicate whether stock is vendor‑backed or channel stock. Explanation: if multiple authorized distributors show short lead times and in‑stock quantities, spot buys are low risk; if supply shifts to long lead times or grey‑market listings with premium pricing, plan multi‑quarter buys and engage sales for firm quotes and allocation.

Sourcing risks: counterfeits, grey market, and obsolescence

Point: Clock ICs are not immune to counterfeiting and grey‑market risks; verification protects production. Evidence: reseller listings (especially on secondary markets) sometimes omit certificate of conformance or show inconsistent markings. Explanation: prefer authorized distributors, request lot traceability and COA, inspect received parts for consistent markings and packaging, and reject units lacking datasheet references or visible lot codes. Consider last‑time‑buy scenarios and identify compatible substitutes early to mitigate obsolescence risk.

4 — Integration & Test Guide: How to Validate SI53361-B-GMR in Your Design (Method/How-to)

Recommended evaluation setup and test plan

Point: A concise eval setup reduces integration risk: high‑bandwidth scope, low‑noise supply, proper terminations and fixtures. Evidence: practical lab experience and vendor evaluation recommendations indicate a minimum bench set of a 1 GHz+ scope, 50 Ω terminations, and a clean 3.3 V supply. Explanation: checklist the hardware—oscilloscope with time‑interval error (TIE) capability for jitter, appropriate probes (low‑capacitance active probes if needed), and controlled‑impedance traces on the eval PCB. Run a planned sequence: visual/continuity checks, power sequencing, basic functional verification, then jitter/skew characterization under expected load.

Common configuration options and register settings

Point: The SI53361 offers OE control and input‑muxing choices for redundancy and fanout flexibility. Evidence: register map excerpts and application notes describe OE behavior and input selection practices. Explanation: implement OE pin logic to control outputs during power sequencing or hot‑swap events, and use the input mux to establish primary/secondary clock failover. For programmable features consult the register map to set output enable patterns and drive-strength options as needed.

Troubleshooting checklist

Point: A short troubleshooting checklist speeds root cause isolation: power rails, decoupling, probe loading, and clock input quality. Evidence: common failure modes documented in vendor QA notes and bench experience include missing outputs due to incorrect VCC or EP soldering, and degraded jitter from poor grounding. Explanation: verify each power rail with scope/probe, confirm EP solder and via connections, inspect decoupling placement, check input amplitude and duty cycle, and rule out probe loading or routing crosstalk before concluding part failure.

5 — Buying Playbook & Next Steps: Procurement Checklist and Recommendations (Case & Action)

Short buying checklist (ready-to-paste for procurement)

Point: A concise, copy‑pasteable checklist accelerates purchasing accuracy. Evidence: combining distributor listing practice with procurement best practices yields this checklist. Explanation: include exact part (SI53361-B-GMR), package (16‑VFQFN, exposed pad), temperature grade, RoHS requirement, MOQ, preferred distributors, request COA and lot traceability, order 5–10 test samples before volume buy and capture timestamped distributor pages for records.

Negotiation & volume pricing strategies

Point: Price vs lead time tradeoffs can be negotiated by bundling, firm quotes, or multi‑quarter commitments. Evidence: distributor quoting behavior and sales practices show reduced unit price for volume commitments or extended lead‑time acceptance. Explanation: request firm quotes with valid‑through dates, negotiate price breaks at realistic volume tiers, and consider consolidating buys across a family of parts to improve leverage. If supply is constrained, evaluate close substitutes within the Si5336x family for C‑class substitution after compatibility checks.

Post-purchase verification & inventory best practices

Point: Receiving inspection, test‑program verification and inventory controls reduce production risk. Evidence: standard incoming inspection and traceability procedures applied to timing ICs catch mismatches early. Explanation: on receipt, verify label and lot against PO, run the part through a short functional test (OE, output levels, frequency), label and store per shelf‑life recommendations, and set reorder triggers based on BOM criticality and distributor lead‑time to maintain a safety stock.

Summary

- SI53361-B-GMR is a compact 2:8 clock buffer with low jitter and low skew, offered in a 16‑VFQFN exposed‑pad package—well suited for board‑level clock distribution in networking, storage, and FPGA/SoC systems.

- Current US distributor snapshots indicate broad availability with typical unit pricing around $2.49–$3.50; capture timestamped listings for procurement records and lifecycle checks.

- Follow PCB exposed‑pad soldering, thermal‑via, decoupling and routing best practices; verify timing with a high‑bandwidth scope and run a short functional test before volume deployment.

- Procurement checklist: use exact part number, request COA/lot traceability, order test samples, and negotiate firm quotes for volume buys to manage price and lead‑time risk.

FAQ — Where to buy SI53361-B-GMR in stock?

Point: Authorized distributors are the primary sources; specialized resellers may offer immediate stock but require vetting. Evidence: major US distributors routinely list SI53361 family parts and show stock/lead‑time details. Explanation: prioritize Digi‑Key, Mouser and Arrow for traceability and COA; if using a smaller reseller request lot traceability and inspect packaging and markings on receipt to avoid counterfeit or grey‑market risks.

FAQ — What specs should I verify from the SI53361-B-GMR datasheet?

Point: Verify supply voltage, IO logic levels, jitter/skew figures, thermal pad recommendations and absolute maximum ratings. Evidence: datasheet sections list operating conditions, timing tables and PCB recommendations. Explanation: use the datasheet numbers for exact current consumption, recommended decoupling, VCC sequence and thermal via counts; if any datasheet note is unclear, request clarification from the vendor or distributor technical support before production.

FAQ — How to validate jitter and skew for SI53361-B-GMR in my system?

Point: Use a high‑bandwidth scope or jitter analyzer, proper termination, and repeatable fixtures to measure device contribution. Evidence: lab best practices and vendor measurement notes emphasize instrument bandwidth, probe selection and averaging. Explanation: ensure scope bandwidth ≥3× maximum signal frequency (1 GHz recommended for 200 MHz clocks), use low‑capacitance probes, measure TIE or RMS jitter with repeatable fixtures, and factor fixture/board contributions into the system jitter budget when comparing to datasheet figures.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606